# Actel Mask Programmed Gate Arrays

#### Features

- Mask Programmed versions of Actel Field Programmable Gate Arrays (FPGAs)

- Significant cost reduction for medium- to high-volume applications

- Pin-for-pin compatible with Actel FPGAs

- PCI Local Bus Revision 2 Compliant

- Automatic translation from Actel FPGA netlist to MPGA

- · Test vectors generated from customer simulation vectors

- · Short lead times for prototype and production devices

- MPGA available for all ACT 1, ACT 2, 1200XL, ACT 3, and 3200DX devices

- Device sizes from 1,200 to 10,000 gates

- Up to 175 user I/Os

# **Product Family Profile**

- Available in commercial or industrial temperature ranges

- PLCC, PQFP, VQFP, and TQFP packages available

- Meets all internal worst-case FPGA performance specifications

- Lower I/O capacitance than FPGA

- · Lower power dissipation than FPGA

#### Description

The Actel Mask Programmed Gate Array (MPGA) products are masked versions of the popular Actel FPGA families. These semi-custom devices offer the customer a design path that provides significant cost reduction without significant risk or engineering effort. For medium- to high-volume applications in which the design is fixed, the Actel FPGA used for prototyping and initial production can be replaced by the corresponding MPGA device.

|                        |                                   | Сара                       | acity                   |                        | Available F       | Packages             |         |         |

|------------------------|-----------------------------------|----------------------------|-------------------------|------------------------|-------------------|----------------------|---------|---------|

| MPGA<br>Device<br>Type | Gate Array<br>Equivalent<br>Gates | PLD<br>Equivalent<br>Gates | Flip-Flops<br>(Maximum) | User I/Os<br>(Maximum) | PLCC              | PQFP                 | VQFP    | TQFP    |

| M1010                  | 1,200                             | 3,000                      | 147                     | 57                     | 44, 68-pin        | 100-pin              | 80-pin  | _       |

| M1020                  | 2,000                             | 6,000                      | 273                     | 69                     | 44, 68,<br>84-pin | 100-pin              | 80-pin  | —       |

| M1225                  | 2,500                             | 6,250                      | 382                     | 83                     | 84-pin            | 100-pin              | 100-pin | —       |

| M1240                  | 4,000                             | 10,000                     | 568                     | 104                    | 84-pin            | 100, 144-pin         | —       | 176-pin |

| M1280                  | 8,000                             | 20,000                     | 998                     | 140                    | 84-pin            | 100, 160,<br>208-pin | —       | 176-pin |

| M1415                  | 1,500                             | 3,750                      | 312                     | 80                     | 84-pin            | 100-pin              | 100-pin | —       |

| M1425                  | 2,500                             | 6,250                      | 435                     | 100                    | 84-pin            | 100, 160-pin         | 100-pin | —       |

| M1440                  | 4,000                             | 10,000                     | 706                     | 140                    | 84-pin            | 160-pin              | 100-pin | 176-pin |

| M1460                  | 6,000                             | 15,000                     | 976                     | 167                    | —                 | 160, 208-pin         | —       | 176-pin |

| M14100                 | 10,000                            | 25,000                     | 1153                    | 175                    | —                 | 208-pin              | —       | —       |

| M3265                  | 6,500                             | 1,600                      | 747                     | 126                    | 84-pin            | 100, 160-pin         |         | 176-pin |

| M32100                 | 10,000                            | 25,000                     | 1031                    | 152                    | 84-pin            | 160, 208-pin         | —       | 176-pin |

| M32140                 | 14,000                            | 35,000                     | 1410                    | 176                    | 84-pin            | 160, 208-pin         | —       | 176-pin |

| M32200                 | 20,000                            | 50,000                     | 1822                    | 202                    | —                 | 208, 240-pin         | —       | —       |

| M32300                 | 30,000                            | 75,000                     | 2804                    | 250                    | —                 | 208, 240-pin         | —       | —       |

| M32400                 | 40,000                            | 100,000                    | 3759                    | 288                    | _                 | 240-pin              | —       | —       |

The granular, regular structure of the Actel antifuse-based FPGA products enables easy conversion to MPGA. Actel provides all required engineering services to convert the customer design from FPGA to MPGA, using proprietary software to automatically convert the FPGA logic design into the MPGA device. Test vector generation is made easy by software that converts the customer's third-party simulation vectors into the final vectors used to test the device in production.

All Actel MPGA devices are pin-for-pin compatible with the corresponding FPGA, and therefore no board redesign is required. MPGA devices meet all worst-case timing specifications of the FPGA devices. MPGA devices are available for all plastic packaged devices from ACT 1, ACT 2, 1200XL, ACT 3, and 3200DX families. See the "Product Plan" on page 1-260 for a detailed list of available device and package combinations.

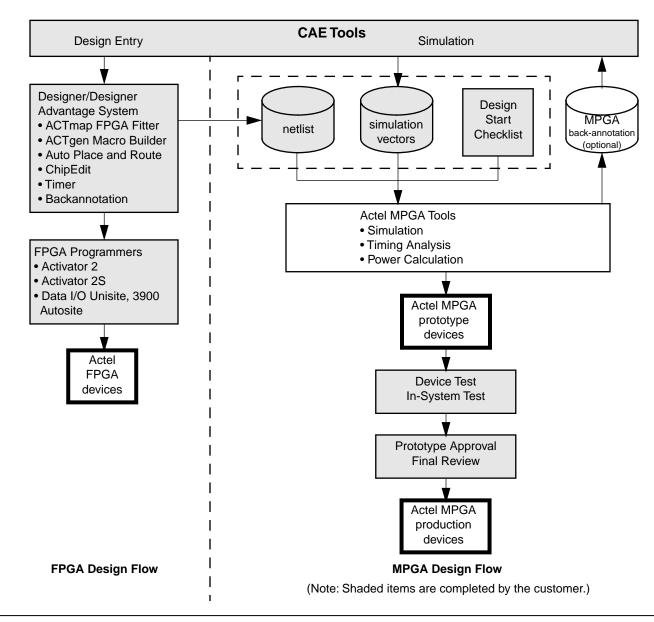

#### Actel FPGA to MPGA Design Flow

Actel's three families of FPGA devices offer a wide selection of device sizes, package choices, performance characteristics, and price points. The FPGA families provide the ideal prototyping tool and are cost-effective for low- to medium-volume applications. As volumes increase, a cost-reduction path becomes a key factor to ensure continued success and profitability of the end product. Once the design has stabilized and volumes are increasing, a choice can be made to convert the design to an MPGA. Since the MPGA product is pin-for-pin compatible with the FPGA, no board redesign is required, and the MPGA can directly replace the FPGA.

A typical design process uses the FPGA device as the prototyping and initial production product of choice and converts to the MPGA as volumes warrant. Figure 1 shows the design process for Actel FPGA and MPGA devices. This option gives you the flexibility to adjust volumes as the demand for the end product changes. Since the MPGA is a semicustom device, all production is built to your order. If the design is already completed in the FPGA, any demand upsides can be satisfied by temporarily switching production back to the FPGA. Since Actel FPGAs are standard off-the-shelf devices, additional product requirements can be met within a short lead time.

The Actel FPGA devices offer the easiest and fastest way to bring a new product to market, and the three FPGA families offer a wide selection of low-cost, high-performance devices. The addition of the MPGA devices offers a simple, low-risk cost-reduction path as production volumes increase.

Figure 1 • Actel Device Design Flow

#### **Product Plan**

|                                                                                        | Availability | Applic       | ation        |  |

|----------------------------------------------------------------------------------------|--------------|--------------|--------------|--|

| ACT 1 Family                                                                           |              | Commercial   | Industrial   |  |

| M1010 Device                                                                           |              |              |              |  |

| 44-pin Plastic Leaded Chip Carrier (PLCC)                                              | V            | V            | ~            |  |

| 68-pin Plastic Leaded Chip Carrier (PLCC)                                              | $\checkmark$ | $\checkmark$ | ~            |  |

| 80-pin Very Thin Plastic Quad Flatpack (VQFP)                                          | ~            | ~            | _            |  |

| 100-pin Plastic Quad Flatpack (PQFP) M1020 Device                                      | <i>v</i>     | <i>v</i>     | ~            |  |

|                                                                                        |              |              |              |  |

| 44-pin Plastic Leaded Chip Carrier (PLCC)<br>68-pin Plastic Leaded Chip Carrier (PLCC) |              | V            |              |  |

| 80-pin Very Thin Plastic Quad Flatpack (VQFP)                                          | v<br>v       | v<br>v       | <b>v</b>     |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)                                              | ~            | ~            | ~            |  |

| 100-pin Plastic Quad Flatpack (PQFP)                                                   | v            | v            | ~            |  |

| ACT 2/1200XL Family                                                                    |              |              |              |  |

| M1225 Device                                                                           |              |              |              |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)                                              | ✓            | ✓            | ✓            |  |

| 100-pin Plastic Quad Flatpack (PQFP)                                                   | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| 100-pin Thin Plastic Quad Flatpack (TQFP)                                              | V            | v            |              |  |

| M1240 Device                                                                           |              |              |              |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)                                              | V            | V            | ~            |  |

| 100-pin Plastic Quad Flatpack (PQFP)                                                   | V            | V            |              |  |

| 144-pin Plastic Quad Flatpack (PQFP)<br>176-pin Thin Plastic Quad Flatpack (TQFP)      | V            | V            | <i>v</i>     |  |

| M1280 Device                                                                           | •            | •            |              |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)                                              |              | V            |              |  |

| 100-pin Plastic Quad Flatpack (PQFP)                                                   | V<br>V       | v<br>v       | ~            |  |

| 160-pin Plastic Quad Flatpack (PQFP)                                                   | ~            | ~            | ~            |  |

| 176-pin Thin Plastic Quad Flatpack (TQFP)                                              | ~            | ~            |              |  |

| ACT 3 Family                                                                           |              |              |              |  |

| M1415 Device                                                                           |              |              |              |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)                                              | <b>v</b>     | <b>v</b>     | ~            |  |

| 100-pin Plastic Quad Flatpack (PQFP)                                                   | $\checkmark$ | ✓            | ~            |  |

| 100-pin Very Thin Plastic Quad Flatpack (VQFP)                                         | $\checkmark$ | V            |              |  |

| Note:M1425 Device                                                                      |              |              |              |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)                                              | <b>v</b>     | V            | ~            |  |

| 100-pin Plastic Quad Flatpack (PQFP)                                                   | V            | V            | ~            |  |

| 100-pin Very Thin Plastic Quad Flatpack (VQFP)<br>160-pin Plastic Quad Flatpack (PQFP) |              |              | ~            |  |

| M1440 Device                                                                           | •            | •            | •            |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)                                              | <b>v</b>     | V            | ~            |  |

| 100-pin Very Thin Plastic Quad Flatpack (VQFP)                                         | · ·          | ~            | -<br>-       |  |

| 160-pin Plastic Quad Flatpack (PQFP)                                                   | ✓            | <b>v</b>     | ~            |  |

| 176-pin Thin Plastic Quad Flatpack (TQFP)                                              | V            | ✓            | —            |  |

| M1460 Device                                                                           |              |              |              |  |

| 160-pin Plastic Quad Flatpack (PQFP)                                                   | ✓            | ~            | ~            |  |

| 176-pin Thin Plastic Quad Flatpack (TQFP)                                              | V            | <b>V</b>     |              |  |

| 208-pin Plastic Quad Flatpack (PQFP)                                                   | V            | <i>v</i>     | <b>v</b>     |  |

| M14100 Device                                                                          |              |              |              |  |

| 208-pin Plastic Quad Flatpack (PQFP)                                                   | ~            | ~            | ~            |  |

#### Product Plan (continued)

|                                                       | Availability          | Application           |                       |  |

|-------------------------------------------------------|-----------------------|-----------------------|-----------------------|--|

| 3200DX Family                                         |                       |                       |                       |  |

| M3265 Device                                          |                       |                       |                       |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)             | <ul> <li>✓</li> </ul> | <ul> <li>✓</li> </ul> | <ul> <li>✓</li> </ul> |  |

| 100-pin Plastic Quad Flatpack (PQFP)                  | ~                     | <ul> <li>✓</li> </ul> | ~                     |  |

| 160-pin Plastic Quad Flatpack (PQFP)                  | ~                     | ✓                     | ~                     |  |

| 176-pin Thin Plastic Quad Flatpack (TQFP)             | $\checkmark$          | ✓                     | ~                     |  |

| M32100 Device                                         |                       |                       |                       |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)             | Р                     | Р                     | Р                     |  |

| 160-pin Plastic Quad Flatpack (PQFP)                  | Р                     | Р                     | Р                     |  |

| 208-pin Plastic Quad Flatpack (PQFP)                  | Р                     | Р                     | Р                     |  |

| 176-pin Thin Plastic Quad Flatpack (TQFP)             | Р                     | Р                     | Р                     |  |

| M32140 Device                                         |                       |                       |                       |  |

| 84-pin Plastic Leaded Chip Carrier (PLCC)             | <ul> <li>✓</li> </ul> | <ul> <li>✓</li> </ul> | ~                     |  |

| 160-pin Plastic Quad Flatpack (PQFP)                  | ~                     | <b>v</b>              | ~                     |  |

| 208-pin Plastic Quad Flatpack (PQFP)                  | ~                     | ✓                     | ~                     |  |

| 176-pin Thin Plastic Quad Flatpack (TQFP)             | $\checkmark$          | ✓                     | ~                     |  |

| M32200 Device                                         |                       |                       |                       |  |

| 208-pin Plastic Quad Flatpack (PQFP)                  | <ul> <li>✓</li> </ul> | <ul> <li>✓</li> </ul> | <b>v</b>              |  |

| 240-pin Plastic Quad Flatpack (PQFP)                  | $\checkmark$          | ✓                     | ~                     |  |

| 176-pin This Plastic Quad Flatpack (TQFP)             | <ul> <li>✓</li> </ul> | V                     | ~                     |  |

| M32300 Device                                         |                       |                       |                       |  |

| 208-pin Plastic Quad Flatpack (PQFP)                  | <ul> <li>✓</li> </ul> | <ul> <li>✓</li> </ul> | ~                     |  |

| 240-pin Plastic Quad Flatpack (PQFP)                  | $\checkmark$          | ✓                     | ~                     |  |

| Availability: $\checkmark$ = Available<br>P = Planned |                       |                       |                       |  |

— = Not Planned

# **ACT 1 Device Resources**

|             |                            | User I/Os |        |        |         |        |  |  |  |

|-------------|----------------------------|-----------|--------|--------|---------|--------|--|--|--|

| MPGA        | Gate Array<br>A Equivalent |           | PLCC   | PQFP   | VQFP    |        |  |  |  |

| Device Type | Gates                      | 44-pin    | 68-pin | 84-pin | 100-pin | 80-pin |  |  |  |

| M1010       | 1200                       | 34        | 57     | 57     | 57      | 57     |  |  |  |

| M1020       | 2000                       | 34        | 57     | 69     | 69      | 69     |  |  |  |

# ACT 2/1200XL Device Resources

| MPGA        | Gate Array<br>MPGA Equivalent |        | PLCC PQFP |         |         |         |         | TQFP    |

|-------------|-------------------------------|--------|-----------|---------|---------|---------|---------|---------|

| Device Type | Gates                         | 84-pin | 100-pin   | 144-pin | 160-pin | 208-pin | 100-pin | 176-pin |

| M1225       | 2500                          | 72     | 83        | —       | —       | —       | 83      | —       |

| M1240       | 4000                          | 72     | 83        | 104     | _       | _       | _       | 104     |

| M1280       | 8000                          | 72     | 83        |         | 125     | 140     |         | 140     |

#### ACT 3 Device Resources

|             |                          | User I/Os |         |         |         |         |         |

|-------------|--------------------------|-----------|---------|---------|---------|---------|---------|

| MPGA        | Gate Array<br>Equivalent | PLCC      |         | PQFP    |         | VQFP    | TQFP    |

| Device Type | Gates                    | 84-pin    | 100-pin | 160-pin | 208-pin | 100-pin | 176-pin |

| M1415       | 1500                     | 70        | 80      | _       | _       | 80      | —       |

| M1425       | 2500                     | 70        | 80      | 100     | _       | 83      | —       |

| M1440       | 4000                     | 70        | —       | 131     | _       | 83      | 140     |

| M1460       | 6000                     | —         | —       | 131     | 167     | —       | 151     |

| M14100      | 10000                    | —         | —       |         | 175     | —       | —       |

#### **3200DX Device Resources**

|             |                     | User I/Os |           |         |         |         |         |

|-------------|---------------------|-----------|-----------|---------|---------|---------|---------|

| MPGA        | Gate Array          |           | PLCC PQFP |         |         |         |         |

| Device Type | Equivalent<br>Gates | 84-pin    | 100-pin   | 160-pin | 208-pin | 240-pin | 176-pin |

| M3265       | 6500                | 72        | 83        | 125     | _       | _       | 126     |

| M32100      | 10000               | 72        | —         | 125     | 156     | _       | 151     |

| M32140      | 14000               | 72        | —         | 125     | 176     | _       | 151     |

| M32200      | 20000               | —         | —         | —       | 176     | TBD     | —       |

| M32300      | 30000               | —         | —         | —       | 176     | TBD     | —       |

| M32400      | 40000               | —         | —         |         | —       | TBD     | —       |

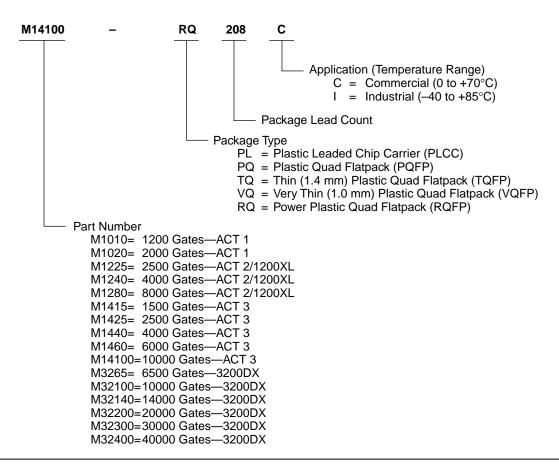

#### **Ordering Information**

# Absolute Maximum Ratings<sup>1</sup>

#### Free air temperature range

| V  |

|----|

| V  |

| V  |

| mA |

| °C |

|    |

Note:

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the Recommended Operating Conditions.

#### **Recommended Operating Conditions**

| Parameter                 | Commercial | Industrial | Units            |

|---------------------------|------------|------------|------------------|

| Temperature Range         | 0 to +70   | -40 to +85 | °C               |

| Power Supply<br>Tolerance | ±5         | ±10        | %V <sub>CC</sub> |

|                                |                              |                                     | Com  | nmercial              | Inc  | lustrial              |       |

|--------------------------------|------------------------------|-------------------------------------|------|-----------------------|------|-----------------------|-------|

| Symbol                         | Parameter                    | Test Condition                      | Min. | Max.                  | Min. | Max.                  | Units |

| V <sub>OH</sub> <sup>1,2</sup> | HIGH Level Output            | I <sub>OH</sub> = -6 mA (CMOS)      | 3.7  | •                     | 3.7  | •                     | V     |

|                                |                              | $I_{OH} = -8 \text{ mA} (TTL)^3$    | 2.4  |                       | 2.4  |                       | V     |

| V <sub>OL</sub> <sup>1,2</sup> | LOW Level Output             | I <sub>OL</sub> = +6 mA (CMOS)      |      | 0.4                   |      | 0.4                   | V     |

|                                |                              | $I_{OL}$ = +8 mA (TTL) <sup>3</sup> |      | 0.4                   |      | 0.4                   | V     |

| V <sub>IH</sub>                | HIGH Level Input             | TTL Inputs                          | 2.0  | V <sub>CC</sub> + 0.3 | 2.0  | V <sub>CC</sub> + 0.3 | V     |

| V <sub>IL</sub>                | LOW Level Input              | TTL Inputs                          | -0.3 | 0.8                   | -0.3 | 0.8                   | V     |

| I <sub>IN</sub>                | Input Leakage                | $V_{I} = V_{CC} \text{ or } GND$    | -1   | +1                    | -1   | +1                    | μΑ    |

| I <sub>OZ</sub>                | 3-state Output Leakage       | $V_{O} = V_{CC}$ or GND             | -10  | +10                   | -10  | +10                   | μΑ    |

| C <sub>IO</sub>                | I/O Capacitance <sup>3</sup> |                                     |      | 10                    |      | 10                    | pF    |

| I <sub>CC(S)</sub>             | Standby Supply Current       | $V_{I} = V_{CC}$ or GND,            |      |                       |      |                       |       |

|                                |                              | I <sub>O</sub> = 0 mA               |      | 100                   |      | 500                   | μA    |

# **Electrical Specifications**

Notes:

1. Actel devices can drive and receive either CMOS or TTL signal levels. No assignment of I/Os as TTL or CMOS is required.

2. Tested one output at a time,  $V_{CC} = min$ .

3. Not tested, for information only.

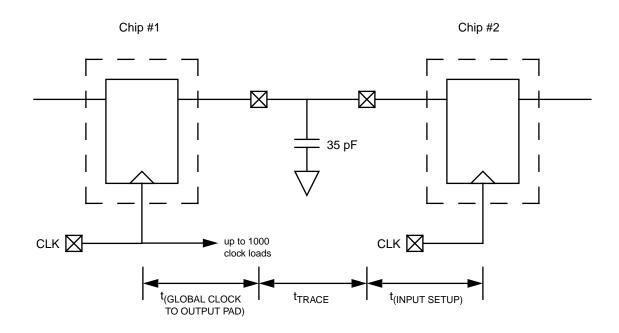

# **Chip-to-Chip Performance**

|            | Chip-to-Chip Performance<br>(Worst-Case Commercial) |                    |                |       |     |  |

|------------|-----------------------------------------------------|--------------------|----------------|-------|-----|--|

|            | <sup>t</sup> (GLOBAL CLOCK<br>TO OUPUT PAD)         | t <sub>TRACE</sub> | t(INPUT SETUP) | Total | MHz |  |

| Actel MPGA | 12.7                                                | 1.0                | 3.1            | 16.8  | 60  |  |

#### **Pin Description**

Package pin assignments for an FPGA design are directly transferred to the equivalent MPGA package because all I/O and power pins are located in identical positions. While the conversion of package pin assignments is transparent in the end product, there are two small functional differences to

note between the device types. First, dedicated FPGA global and debugging pins are general purpose MPGA I/O pins. Also, dedicated FPGA programming voltage pins are Vcc or ground pins on an MPGA. Refer to Table 1 for a complete cross-reference of pin descriptions between the FPGA and MPGA.

Table 1

FPGA-to-MPGA Pin Cross-Reference

| FPGA Pin Description                                                                                                                                                                                          |               | MPGA Pin Description                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CLK Clock (ACT 1 only)</b><br>TTL Clock input for ACT 1 global clock distribution net-<br>work. This pin can also be used as an I/O.                                                                       | $\rightarrow$ | <b>No Change</b><br>If desired, TTL Clock input signals may be moved to any<br>MPGA I/O location.                                                 |

| CLKAClock A (ACT 3, 3200DX, 1200XL, and ACT 2<br>only)TTL Clock input for clock distribution networks. This pin<br>can also be used as an I/O.                                                                | $\rightarrow$ | <b>No Change</b><br>If desired, TTL Clock input signals may be moved to any<br>MPGA I/O location.                                                 |

| CLKBClock B (ACT 3, 3200DX, 1200XL, and ACT 2<br>only)TTL Clock input for clock distribution networks. This pin<br>can also be used as an I/O.                                                                | $\rightarrow$ | <b>No Change</b><br>If desired, TTL Clock input signals may be moved to any<br>MPGA I/O location.                                                 |

| <b>DCLK Diagnostic Clock</b><br>TTL Clock input for diagnostic probe and device program-<br>ming. Function is controlled by the MODE pin.                                                                     | $\rightarrow$ | <b>I/O</b><br>This pin is used as an I/O only. It is not used for diagnos-<br>tic probe or device programming functions on an MPGA.               |

| GND Ground<br>LOW supply voltage.                                                                                                                                                                             | $\rightarrow$ | Ground<br>LOW supply voltage.                                                                                                                     |

| HCLKDedicated (Hard-wired) Array Clock<br>(ACT 3 only)TTL Clock input for ACT 3 sequential modules. This pin<br>can also be used as an I/O.                                                                   | $\rightarrow$ | <b>No Change</b><br>If desired, TTL Clock input signals may be moved to any<br>MPGA I/O location.                                                 |

| <b>I/O</b> Input/Output<br>The I/O pin functions as an input, output, three-state, or<br>bidirectional buffer. Unused pins are automatically driven<br>LOW by the Designer software.                          | $\rightarrow$ | <b>I/O</b><br>User-defined MPGA I/O pins function identically to their<br>FPGA counterparts. However, unused pins are NC (no<br>connection) pins. |

| IOCLK Dedicated (Hard-wired) I/O Clock<br>(ACT 3 only)<br>TTL Clock input for ACT 3 I/O modules. This pin can also<br>be used as an I/O.                                                                      | $\rightarrow$ | <b>No Change</b><br>If desired, TTL Clock input signals may be moved to any<br>MPGA I/O location.                                                 |

| IOPCL Dedicated (Hard-wired) I/O Preset/Clear<br>(ACT 3 only)<br>TTL input for ACT 3 I/O preset or clear. This pin can also<br>be used as an I/O.                                                             | $\rightarrow$ | <b>No Change</b><br>If desired, this input signal may be moved to any MPGA<br>I/O location.                                                       |

| <b>MODE Mode</b><br>The MODE pin controls the use of diagnostic pins (DCLK, PRA, PRB, SDI). When the MODE pin is HIGH, the special functions are active. When the MODE pin is LOW, the pins function as I/Os. | $\rightarrow$ | <b>TEST (No Connection)</b><br>This pin is reserved for parametric testing and should be<br>connected to ground (LOW supply voltage).             |

# Table 1 FPGA-to-MPGA Pin Cross-Reference (continued)

| FPGA Pin Description                                                                                                                                                                                      | MPGA Pin Description                                                                                                                                  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NCNo ConnectionThis pin is not connected to circuitry within the device.                                                                                                                                  | $ \rightarrow \begin{array}{cc} \text{NC} & \text{No Connection} \\ \\ \text{This pin is not connected to circuitry within the device.} \end{array} $ |  |  |  |

| PRAProbe AThe Probe A pin is used for FPGA diagnostics. Functionis controlled by the MODE pin.                                                                                                            | <ul> <li>I/O</li> <li>→ This pin is used as an I/O only. It is not used for diagnostic probe or device programming functions on an MPGA.</li> </ul>   |  |  |  |

| PRBProbe BThe Probe B pin is used for FPGA diagnostics. Functionis controlled by the MODE pin.                                                                                                            | <ul> <li>I/O</li> <li>→ This pin is used as an I/O only. It is not used for diagnostic probe or device programming functions on an MPGA.</li> </ul>   |  |  |  |

| QCLKA/B,C,DQuadrant Clock (Input/Output)<br>(3200DX only)These four pins are the quadrant clock inputs. When not<br>used as a register control signal, these pins can function<br>as general purpose I/O. | → No Change<br>If desired, TTL Clock input signals may be moved to any<br>MPGA location.                                                              |  |  |  |

| SDISerial Data InputSerial data input for diagnostic probe and device pro-<br>gramming. Function is controlled by the MODE pin.                                                                           | → I/O<br>This pin is used as an I/O only. It is not used for diagnos-<br>tic probe or device programming functions on an MPGA.                        |  |  |  |

| TCKTest Clock (3200DX only)Clock signal to shift the JTAG data into the device. This<br>pin functions as an I/O when the JTAG fuse is not pro-<br>grammed                                                 | ightarrow No Change                                                                                                                                   |  |  |  |

| TDITest Data In (3200DX only)Serial data input or JTAG instructions and data. Data is<br>shifted in on the rising edge of TCLK. This pin functions<br>as an I/O when the JTAG fuse is not programmed.     | ightarrow No Change                                                                                                                                   |  |  |  |

| TDOTest Data Out (3200DX only)Serial data output for JTAG instructions and test data.This pin functions as an I/O when the JTAG fuse is notprogrammed.                                                    | ightarrow No Change                                                                                                                                   |  |  |  |

| TMSTest Mode Select (3200DX only)Serial data input for JTAG test mode. Data is shifted in on<br>the rising edge of TCLK. This pin functions as an I/O<br>when the JTAG fuse is not programmed.            | ightarrow No Change                                                                                                                                   |  |  |  |

| V <sub>CC</sub> Supply Voltage<br>HIGH supply voltage.                                                                                                                                                    | $ ightarrow egin{array}{c} {f V}_{CC} \ {f HIGH supply voltage.} \end{array}$                                                                         |  |  |  |

#### **MPGA** Architecture

The Actel MPGA is built using a "sea-of-gates" architecture. A solid, regularly ordered array of transistors is overlaid with a multilevel metal interconnect. Surrounding this logic core is an array of programmable power and I/O pads. Separate grids provide power and ground supplies for the core logic and I/O cells.

The highly dense structure of Actel MPGAs provides for a cost-effective solution while maintaining the high performance of each particular design. This architecture reduces die size for low cost while minimizing gate length and shortening routing paths for excellent system performance. The robust power supply grids provide high I/O current drive without sacrificing high noise immunity. Since Actel FPGAs use a similar gate array architecture, design migration is a straightforward, simple process. Because of the advanced technology employed by the MPGA, the internal and external performance of each design is virtually assured to be preserved or improved after migration. To simplify migration further, the I/O pads are carefully arranged to allow FPGA pin assignments to be directly transferred to the full line of MPGA packages. For more information about the ease of design migration from Actel FPGAs to MPGAs, see the application note "Designing for Migration to Actel MPGAs."

#### **Power Dissipation**

The power dissipation for an Actel MPGA is composed of two parts: static power and active power. The static power is a product of the standby supply current (Icc) and the DC supply voltage (Vcc). Specifications for Icc and Vcc are located in the "Electrical Specifications" section of this data sheet. The active power is a product of equivalent capacitance, square of the DC supply voltage, and average switching frequency of the circuit. It is expressed in the formula

Power ( $\mu$ W) = C<sub>EQ</sub> • V<sub>CC</sub><sup>2</sup> • f

where

C<sub>EQ</sub> is the equivalent capacitance in picofarads (pF)

V<sub>CC</sub> is the DC supply voltage in volts (V)

f is the switching frequency in megahertz (MHz)

Upon receipt of the "Design Start Checklist" and associated materials, Actel calculates the MPGA active power dissipation for each design based on this formula. This calculation is immediately relayed to you so that you can update system power specifications accordingly. Typically, power dissipation of an Actel design is significantly lower for the MPGA version versus the FPGA version.

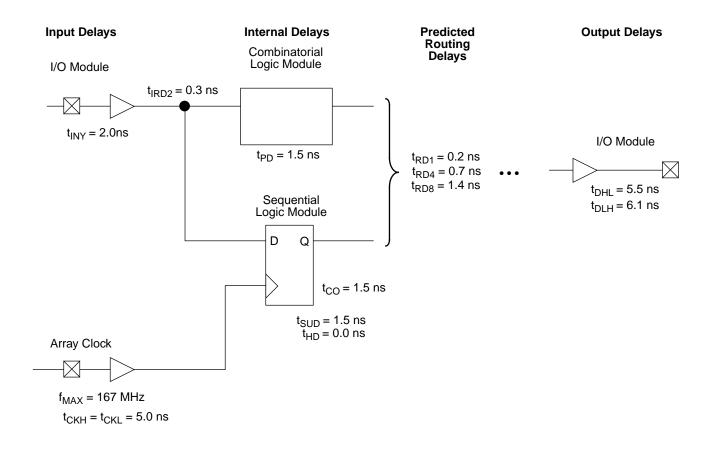

#### **Timing Characteristics**

The timing characteristics for Actel MPGA devices are consistent across family and device types. Typical I/O buffer, internal logic cell, and internal routing delays are common to all MPGA devices. The advanced technology of the devices ensures converted designs meet or exceed FPGA performance. Refer to the MPGA Timing Model diagram and Timing Characteristics chart for detailed timing and delay estimates.

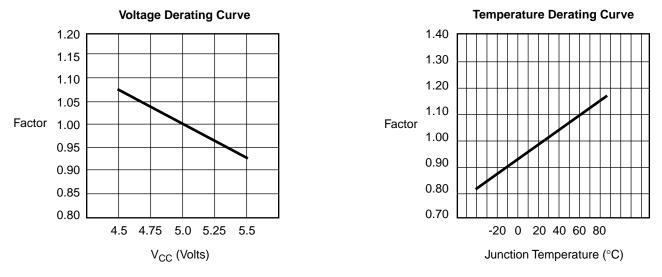

#### **Timing Derating**

Timing derating factors due to temperature, voltage, and process variations are summarized in the following tables and graphs. Use these derating factors to determine device performance at any particular condition within the electrical and environmental specifications.

MPGA devices are manufactured in a CMOS process. Therefore, device performance varies according to temperature, voltage, and process variations. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and best-case processing. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case processing.

#### Timing Derating Factor, Temperature and Voltage

|                                              | Industrial |         |

|----------------------------------------------|------------|---------|

|                                              | Minimum    | Maximum |

| (Commercial Minimum/Maximum Specification) x | 0.85       | 1.07    |

# Timing Derating Factor for Designs at Typical Temperature (T $_J$ = 25°C) and Voltage (V $_{CC}$ = 5.0 V)

| (Commercial Maximum Specification) x | 0.86 |  |

|--------------------------------------|------|--|

|--------------------------------------|------|--|

Note: This derating factor applies to all routing and propagation delays.

#### **MPGA Timing Model**

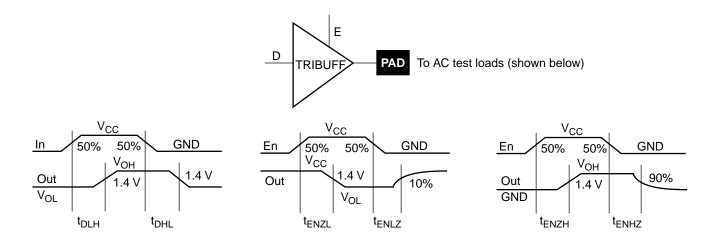

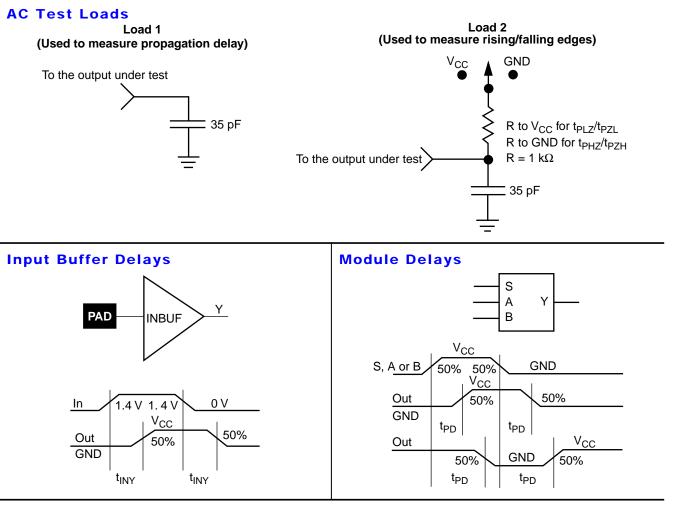

# **Output Buffer Delays**

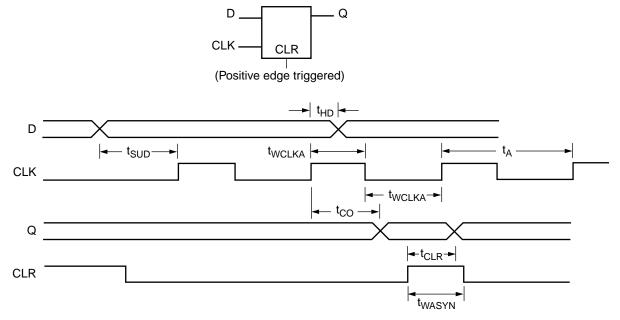

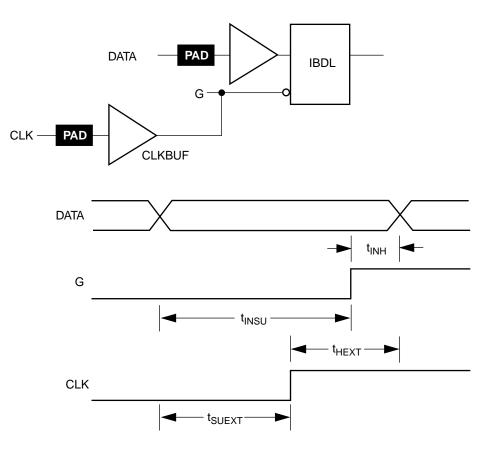

#### **Sequential Module Timing Characteristics**

Flip-Flops

# Sequential Timing Characteristics (continued)

# Input Buffer Latches (3200DX only)

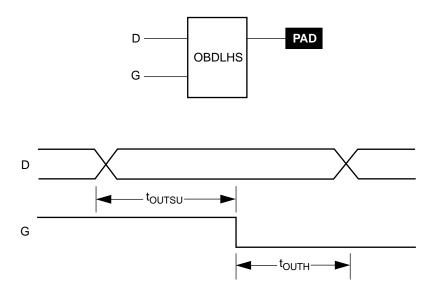

#### Output Buffer Latches (3200DX only)

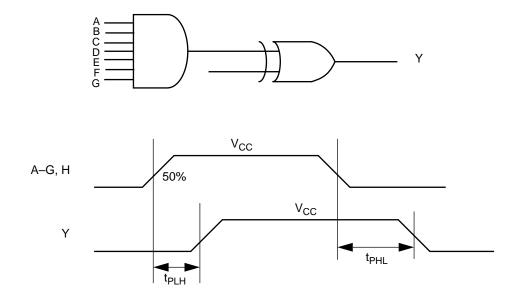

# Decode Module Timing (3200DX only)

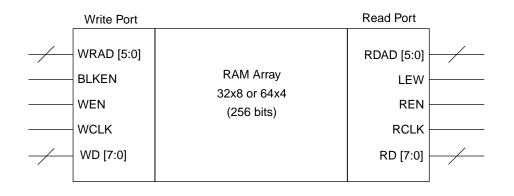

# SRAM Timing Characteristic (3200DX only)

# **Dual-Port SRAM Timing Waveforms**

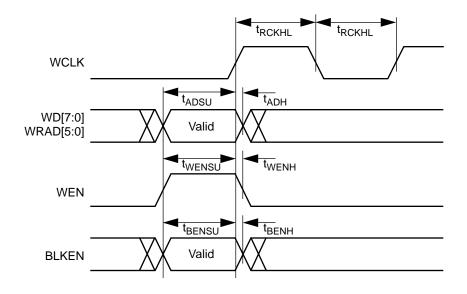

SRAM Write Operation (3200DX only)

#### Note: Identical timing for falling-edge clock.

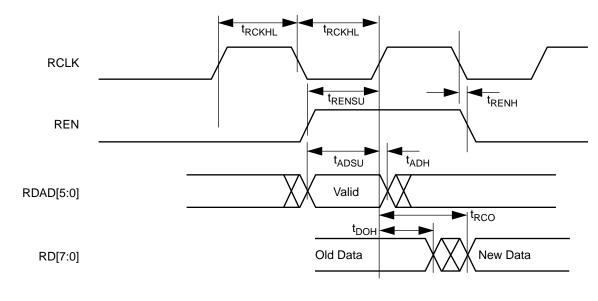

#### SRAM Synchronous Read Operation (3200DX only)

*Note: Identical timing for falling-edge clock*

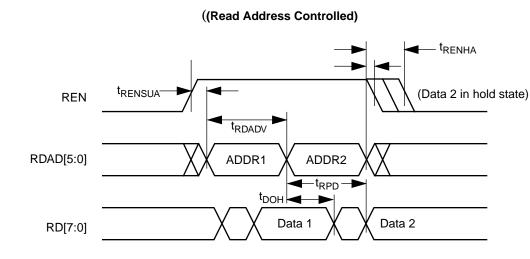

# SRAM Asynchronous Read Operation—Type 1 (3200DX only)

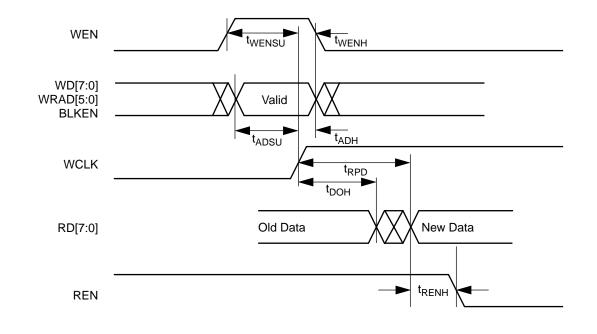

SRAM Asynchronous Read Operation—Type 2 (3200DX only)

(Write Address Controlled)

# **MPGA Timing Characteristics**

|                                 |                              | Preliminary Information |      |       |  |

|---------------------------------|------------------------------|-------------------------|------|-------|--|

| Logic Module Propagation Delays |                              |                         |      |       |  |

| Parameter                       | Description                  | Min.                    | Max. | Units |  |

| t <sub>PD</sub>                 | Internal Array Module        |                         | 1.5  | ns    |  |

| t <sub>CO</sub>                 | Sequential Clock to Q        |                         | 1.5  | ns    |  |

| t <sub>CLR</sub>                | Asynchronous Clear to Q      |                         | 1.5  | ns    |  |

| Predicted Routin                | ng Delays <sup>1</sup>       |                         |      |       |  |

| t <sub>RD1</sub>                | FO=1 Routing Delay           |                         | 0.2  | ns    |  |

| t <sub>RD2</sub>                | FO=2 Routing Delay           |                         | 0.3  | ns    |  |

| t <sub>RD3</sub>                | FO=3 Routing Delay           |                         | 0.5  | ns    |  |

| t <sub>RD4</sub>                | FO=4 Routing Delay           |                         | 0.7  | ns    |  |

| t <sub>RD8</sub>                | FO=8 Routing Delay           |                         | 1.4  | ns    |  |

| Logic Module Se                 | equential Timing             |                         |      |       |  |

| t <sub>SUD</sub>                | Flip-Flop Data Input Setup   | 1.5                     |      | ns    |  |

| t <sub>HD</sub>                 | Flip-Flop Data Input Hold    | 0.0                     |      | ns    |  |

| t <sub>SUD</sub>                | Latch Data Input Setup       | 1.5                     |      | ns    |  |

| t <sub>HD</sub>                 | Latch Data Input Hold        | 0.0                     |      | ns    |  |

| t <sub>WASYN</sub>              | Asynchronous Pulse Width     | 2.0                     |      | ns    |  |

| t <sub>WCLKA</sub>              | Flip-Flop Clock Pulse Width  | 2.0                     |      | ns    |  |

| t <sub>A</sub>                  | Flip-Flop Clock Input Period | 8.0                     |      | ns    |  |

| f <sub>MAX</sub>                | Flip-Flop Clock Frequency    |                         | 125  | MHz   |  |

| I/O Module Input                | t Propagation Delay          |                         |      |       |  |

| t <sub>INY</sub>                | Input Data Pad to Y          |                         | 2.0  | ns    |  |

| Predicted Input                 | Routing Delays <sup>1</sup>  |                         |      |       |  |

| t <sub>IRD1</sub>               | FO=1 Routing Delay           |                         | 0.2  | ns    |  |

| t <sub>IRD2</sub>               | FO=2 Routing Delay           |                         | 0.3  | ns    |  |

| t <sub>IRD3</sub>               | FO=3 Routing Delay           |                         | 0.5  | ns    |  |

| t <sub>IRD4</sub>               | FO=4 Routing Delay           |                         | 0.7  | ns    |  |

| t <sub>IRD8</sub>               | FO=8 Routing Delay           |                         | 1.4  | ns    |  |

#### (Worst-Case Commercial Conditions, $V_{CC}$ = 4.75 V, $T_J$ = 70°C)

Note:

1. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Postroute timing analysis or simulation is required to determine actual worst-case performance. Postroute timing is based on actual routing delay measurements performed on the device prior to shipment.

# MPGA Timing Characteristics (continued)

#### (Worst-Case Commercial Conditions)

|                                             |                                | Preliminary Information |      |       |  |

|---------------------------------------------|--------------------------------|-------------------------|------|-------|--|

| I/O Module – TTL Output Timing <sup>1</sup> |                                |                         |      |       |  |

| Parameter                                   | Description                    | Min.                    | Max. | Units |  |

| t <sub>DHL</sub>                            | Data to Pad, High to Low       |                         | 6.8  | ns    |  |

| t <sub>DLH</sub>                            | Data to Pad, Low to High       |                         | 3.9  | ns    |  |

| t <sub>ENZH</sub>                           | Enable to Pad, Z to High       |                         | 4.5  | ns    |  |

| t <sub>ENZL</sub>                           | Enable to Pad, Z to Low        |                         | 6.8  | ns    |  |

| t <sub>ENHZ</sub>                           | Enable to Pad, High to Z       |                         | 3.8  | ns    |  |

| t <sub>ENLZ</sub>                           | Enable to Pad, Low to Z        |                         | 2.0  | ns    |  |

| d <sub>TLH</sub>                            | Delta Low to High              |                         | 0.05 | ns/pF |  |

| d <sub>THL</sub>                            | Delta High to Low              |                         | 0.09 | ns/pF |  |

| I/O Module – CM                             | IOS Output Timing <sup>1</sup> |                         |      |       |  |

| t <sub>DHL</sub>                            | Data to Pad, High to Low       |                         | 5.5  | ns    |  |

| t <sub>DLH</sub>                            | Data to Pad, Low to High       |                         | 6.1  | ns    |  |

| t <sub>ENZH</sub>                           | Enable to Pad, Z to High       |                         | 6.7  | ns    |  |

| t <sub>ENZL</sub>                           | Enable to Pad, Z to Low        |                         | 5.6  | ns    |  |

| t <sub>ENHZ</sub>                           | Enable to Pad, High to Z       |                         | 3.8  | ns    |  |

| t <sub>ENLZ</sub>                           | Enable to Pad, Low to Z        |                         | 2.0  | ns    |  |

| d <sub>TLH</sub>                            | Delta Low to High              |                         | 0.09 | ns/pF |  |

| d <sub>THL</sub>                            | Delta High to Low              |                         | 0.07 | ns/pF |  |

| Global Clock Ne                             | tworks (for Fanout = 1000)     |                         |      |       |  |

| t <sub>СКН</sub>                            | Input Low to High              |                         | 5.0  | ns    |  |

| t <sub>CKL</sub>                            | Input High to Low              |                         | 5.0  | ns    |  |

| t <sub>PWH</sub>                            | Min. Pulse Width High          | 2.9                     |      | ns    |  |

| t <sub>PWL</sub>                            | Min. Pulse Width Low           | 2.9                     |      | ns    |  |

| t <sub>CKSW</sub>                           | Maximum Skew                   |                         | 0.4  | ns    |  |

| t <sub>P</sub>                              | Minimum Period                 | 6.0                     |      | ns    |  |

| f <sub>MAX</sub>                            | Maximum Frequency              |                         | 167  | MHz   |  |

Note:

1. Delays based on 35pF loading.